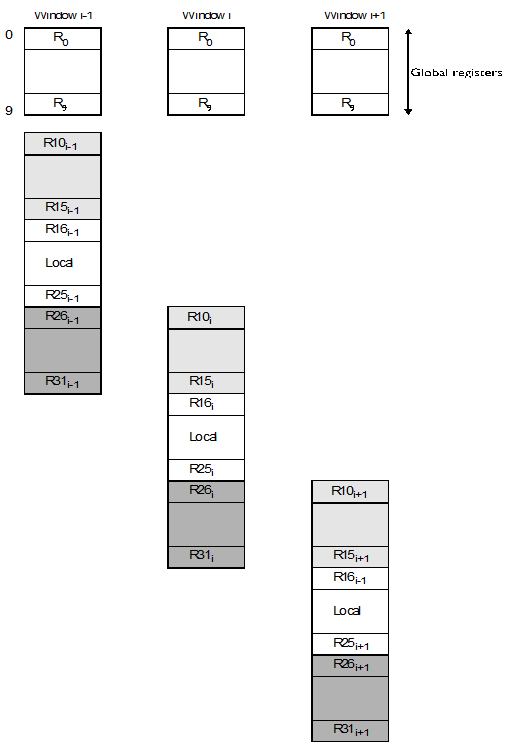

- SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS DRIVERS

- SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS UPDATE

- SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS FULL

- SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS SOFTWARE

- SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS CODE

SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS DRIVERS

With fake hardware drivers and a custom Wimp the old version of RISC OS could be fairly well integrated with the new one, or vice-versa. Run old RISC OS on one core, and the new multicore RISC OS on the others.Moderately easy to get working (hardware drivers would be a bit fiddly), and it would allow users to easily make use of the additional cores, but each program would be limited to running on one core only, and the lack of communication between the different RISC OS instances would make it more similar to using multiple seperate computers than to using just one. Each core runs its own copy of RISC OS in isolation.

SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS SOFTWARE

It also won’t provide much benefits to the user, unless they happen to be running many pieces of software written to take advantage of the extra cores. It would work, and it’s easy to implement, but it’s unlikely to be a solution that is easy for programmers to make good use of. This would be similar to the 2nd processors that used the tube interface of the BBC.

SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS FULL

This would be a very hard and long task, much harder and longer than the OMAP3/BeagleBoard port, and at the end of the day we may end up with something that bares so little resemblence to present-day RISC OS that only the most trivial of existing programs will run without modification.

SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS UPDATE

SUPPOSE THAT A RISC MACHINE USES 5 REGISTER WINDOWS CODE

The fact that the code that’s currently used for preventing concurrent accesses is insufficient, coupled with the fact that shared resource could be almost anything, is the reason why adding multicore support isn’t just a simple case of updating the Wimp to allow two tasks to run at once. This means that all the existing pieces of code that use this method will need updating to use new methods.

But in a multicore environment this simply won’t work – the other cores will continue to run as normal. This ensures that unless something unexpected like a data abort occurs, the current program has 100% control over what the CPU is doing. But no matter what the resource is, the outcome is always the same if two programs/threads/cores fail to negotiate with each other for access: something bad will happen and your data will be corrupted or your programs will crash or malfunction.Īt the moment the most basic method RISC OS uses for preventing concurrent access to a resource is to disable interrupts in the PSR. This shared resource could be almost anything from a physical device like a printer right down to the smallest resource possible, an individual bit of memory. Whenever a core tries to access a shared resources it must make sure that that resource isn’t already in use by another core. This thread intends to be the place for that discussion to take place (plus somewhere for me to point people towards whenever they mention OMAP4 )) The problemįor the uninitiated, the problem with supporting multiple cores is communication. So if we’re serious about the long-term future of RISC OS we need to have some kind of discussion about what our options are with regards to supporting multicore CPUs, so that we can work out what steps we can take to ensure that one day we reach our goal. And those of us who have been watching the CPU market for the last few years are probably in agreement that the days of the high-performance single-core CPU are numbered sooner or later the only high-performance ARM CPUs available will be multicore-only. And I think we all understand that it isn’t likely to be easy to find/implement a solution which is both easy for programmers to make use of and allows the additional cores to be used to their fullest. I think we’re all in agreement that it would be a good thing if RISC OS were able to take advantage of multicore CPUs.

0 kommentar(er)

0 kommentar(er)